### Proceedings of the

### EMerging Technology (EMiT) Conference 2016

2-3 June 2016 Barcelona Supercomputing Center, Spain

Edited by B.D. Rogers, D. Topping, F. Mantovani, M.K. Bane

http://emit.tech

#### Foreword to the 2016 Emerging Technology (EMiT) Conference

Dear Delegate,

The Emerging Tech conference, EMiT, is now firmly established. In its third year we are delighted to be hosted by Barcelona Supercomputing Center and the Mont-Blanc project. BSC has long been held in very high regard, both for its innovative HPC and also its renowned work on advancing new tools for performance analysis and programming models. The presence of the Mont-Blanc project on the EMiT Organising Committee emphasises the growing importance of emerging technologies & techniques to improve the cost and energy efficiency of next generation HPC platforms.

This third EMiT conference follows the philosophy of those preceding by seeking out the challenges of hardware, software, tools and algorithms that we are expecting from over the horizon or are helping create ourselves.

The Organising Committee has overcome many challenges to bring EMiT2016 to fruition. Please join me in extending your appreciation to each of them.

I would also like to thank each keynote, everybody submitting papers (accepted or not), and each sponsor and stall, for showing support to the EMiT series.

We are looking towards EMiT 2017. If you are inspired by this year's conference to host or join the Organising Committee next year then please speak to us.

Michael Bane

Chair, EMiT2016 Organising Committee

http://highendcompute.co.uk

@highendcompute

### **Committee**

### **Organising Committee**

| • | Dr Michael K. Bane    | High End Compute                                                                        |

|---|-----------------------|-----------------------------------------------------------------------------------------|

| • | Dr Filippo Mantovani  | Barcelona Supercomputing Center                                                         |

| • | Renata Gimenez        | Barcelona Supercomputing Center                                                         |

| • | Dr David Topping      | University of Manchester, School of Earth,<br>Atmospheric & Environmental Sciences      |

| • | Dr Stephen Longshaw   | Science & Technology Facilities Council, STFC                                           |

| • | Dr Benedict D. Rogers | University of Manchester, School of Mechanical,<br>Aerospace & Civil Engineering (MACE) |

| • | Irfan Alibay          | University of Manchester, School of Pharmacy                                            |

| • | Ignas Daugalas        | University of Manchester, IT Services                                                   |

| • | Shih-Chen Chao        | University of Manchester, IT Services                                                   |

| • | Prof. Dave Emerson    | Science & Technology Facilities Council, STFC                                           |

#### **Printing**

"The Organising Committee of the 2016 EMiT Conference" shall not be held responsible for any statement or opinion advanced in papers or printed in this volume. The authors' papers have been prepared for final reproduction and printing without any reduction, correction, etc. The authors are fully responsible for all the information contained in their papers.

Copyright © Published by The Emerging Technology (EMiT) Conference Manchester, U.K. ISBN 978-0-9933426-3-9

### **CONTENTS**

| 1: THURSDAY, JUNE 1ST, 2016                                                                                                                                   | 6  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Keynote 1                                                                                                                                                     | 6  |

| W. Sawyer                                                                                                                                                     | 6  |

| Session 1:                                                                                                                                                    | 7  |

| Lee Margetts                                                                                                                                                  | 7  |

| Ahmet Duran, Senol Piskin, Mehmet Tuncel                                                                                                                      | 11 |

| Code modernization of DL_ MESO LBE to achieve good performance on the Intel Xeon Phi  Sergi Siso, Luke Mason, Michael Seaton                                  | 15 |

| Keynote 2                                                                                                                                                     | 19 |

| Chris Adeniyi Jones                                                                                                                                           | 19 |

| Session 2:                                                                                                                                                    | 20 |

| Low-Power, Fault-Resilient Communications in a Million-Core Neural Processing Architecture  Javier Navaridas, Mikel Lujan, Luis A. Plana, Steve B. Furber     | 20 |

| Energy versus performance on low power processors for HPC applications  Enrico Calore, Alessandro Gabbana, Sebastiano Fabio Schifano and Raffaele Tripiccione | 24 |

| Embedding supercomputing at NVIDIA                                                                                                                            |    |

| Alex Ramirez                                                                                                                                                  | 28 |

| DAY 2: FRID | PAY, JUNE 3RD, 2016                                                                                                             | 29 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|----|

|             | Keynote 3                                                                                                                       | 29 |

|             | Michele Weiland                                                                                                                 | 29 |

|             | Session 3:                                                                                                                      | 30 |

|             | Kirsten Eder                                                                                                                    | 30 |

|             | Charles Moulinec, Yvan Fournier, Pascal Vezolle, Benedikt Anlauf  Emerging Technologies for the Convergence of Big Data and HPC | 31 |

|             | Herbert Cornelius                                                                                                               | 35 |

|             | Keynote 4                                                                                                                       | 36 |

|             | Lorena Barba                                                                                                                    | 36 |

|             | Session 4:                                                                                                                      | 37 |

|             | Jianping Meng                                                                                                                   | 37 |

|             | Marc Casas, Mateo Valero                                                                                                        | 41 |

|             | Keynote 5                                                                                                                       | 45 |

|             | Estele Suarez                                                                                                                   | 45 |

|             | Session 5:                                                                                                                      | 46 |

|             | Accelerating High-Throughput Computing through OpenCL  Andrei Dafinoiu, Joshua Higgins, Violeta Holmes                          | 46 |

|             | Energy Efficiency Evaluation in Heterogeneous Computers  Ivan Perez, Esteban Stafford, Ramon Beivide, Jose Luis Bosque          | 50 |

# The Road to Exascale: It's about the Journey not the Flops

William Sawyer

Exa2Green,

Swiss National Supercomputing Centre,

Switzerland

Abstract— One look at the www.top500.org proves it: The exponential growth in supercomputer power has now gone on for decades. Every time physical realities — for example the limits in processor frequency — impinge on this trend, human ingenuity finds workarounds, for example, the evolution of multi-core technology. The hounds have long been barking in the distance, heralding the demise of Moore's Law and reminding us that memory bandwidth is not keeping pace with processing power. And now energy consumption is a key bottleneck: critics correctly point out that a computing center cannot have its own dedicated nuclear power plant. Certainly the HPC advances cannot go on forever.

There is good reason to believe that the trend will continue to Exascale and beyond. Human ingenuity still has the upper hand: new stacked memory offers a new increase in bandwidth; multi-core has given way to many-core, and new processors are effectively reducing energy consumption per Flop. In this talk we present some milestones at the Swiss National Computing Centre. Since the installation of our flagship platform, Piz Daint, we have experimented with new numerical algorithms, developed domain-specific languages, and used new compiler features to refactor codes for its constituent Graphics Processing Units (GPUs) to attain dramatic improvements in time-to-solution and energy-to-solution. We draw the conclusion that HPC is alive and well on its way to Exascale and beyond.

# Parallel finite element analysis using the Intel Xeon Phi

L. Margetts, J. D. Arregui-Mena School of Mechanical, Aerospace and Civil Engineering University of Manchester Manchester, M13 9PL, UK lee.margetts@manchester.ac.uk W. T. Hewitt, L. Mason The Hartree Centre STFC Daresbury Laboratory Daresbury, Cheshire, WA4 4AD, UK

Abstract—This paper describes the porting of the open source engineering software ParaFEM to the Intel Xeon Phi processor. The results of a preliminary performance study are presented for a new open source ParaFEM mini-app written especially for the purpose. The main findings of the study are that: (i) The original MPI-based software scales linearly on up to 56 of the 60 available cores; (ii) A new mixed mode MPI/OpenMP implementation boosts performance by a factor of 4 when using 4 threads per core on 1-16 cores (for the largest problem that fits in the Xeon Phi memory) and (iii) The best Xeon Phi solution time is ~2 times faster than the host; here comprising 2 x 12 core "standard" Intel Xeon processors. It appears that scaling beyond 16 cores and 4 threads per core is limited by the amount of work available to each of the 240 threads. The authors propose a number of strategies that can be explored to reduce the memory footprint of individual finite elements so that a much larger problem can be tackled. With more "parallelizable work" per thread, we expect to be able to further improve the performance of the mixed mode MPI/OpenMP implementation. This work will be of interest to researchers and engineers who may wish to evaluate the Intel Xeon Phi for scientific computing, particularly those using the finite element method.

Keywords—Xeon Phi; finite element analysis; element by element; engineering simulation; mixed MPI/OpenMP; mini-app

#### I. INTRODUCTION

ParaFEM is a parallel library for general purpose finite element analysis that has been written mainly in modern Fortran and uses MPI for message passing. It is supplied with a set of driver programs or "mini-apps" for solving different types of engineering problem. The ParaFEM software comprises a set of libraries for general purpose finite element analysis [1], a library that uses MPI [2] for parallel processing and a set of driver programs or mini-apps for specific types of engineering problem. The mini-apps are concise parallel programs of 2-4 pages in length. The philosophy behind writing mini-apps rather than a monolithic program is that it makes it easier for scientists and engineers to modify the programs for their own use. It also enables parallel computing experts to quickly evaluate strategies for improving performance. The source code for the software is fully documented, both from the point of view of the algorithms used and the meaning of each variable name, in the popular text book "Programming the Finite Element Method" [3].

ParaFEM has been used on various HPC systems including those at the Hartree Centre; the UK's national HPC facilities ARCHER and N8 HPC; as well as systems belonging to the Partnership for Advanced Computing in Europe (PRACE).

Recently published work using ParaFEM involves a number of different scientific application areas including: the characterization of materials for fusion reactors [4]; assessing the structural integrity of nuclear power plants [5]; developing a multiscale modelling platform for fracture using a coupled cellular automata finite element strategy [6] and understanding microstructural deformation in bone [7].

ParaFEM uses a matrix free or element by element method [8]. This works very well in parallelising each stage of the finite element process: general housekeeping (building tables that relate nodes and elements to equations); generating the stiffness matrix for each element; solving the equations (using an element by element form of the Krylov solvers) and computing derived quantities such as stress or strain from the solution vector. No global matrix is ever created and this approach is widely known to be more memory efficient than global matrix assembly and factorization. The implementation therefore seems to suit the small memory footprint (per core) of the Intel Xeon Phi.

For large finite element problems that involve many load steps or time increments, more than 90% of the time is spent in the solver. Drilling down, time in the solver is dominated by large loop count element by element "do loops" of small matrix-vector multiplications. Each matrix represents a single finite element and each vector relates to the element part of the global solution vector. Getting good performance on the Xeon Phi (and other types of hardware) therefore requires optimising this part of the computation.

#### II. PORTING AND OPTIMISATION

#### A. Hardware

This research was carried out using the iDataPlex system hosted at The Hartree Centre in the UK. The system comprises 84 nodes, each with 2 x 12 core Intel Xeon processors (Ivy Bridge E5-2697v2 2.7GHz). 42 of the nodes have an Intel Xeon Phi 5110P accelerator. Each Xeon Phi has 60 cores running at 1.052GHz and can support 4x threads per core.

#### B. Software

A new mini-app was written to help evaluate the performance of ParaFEM on the Xeon Phi. This was given the name xx16 and can be found in the ParaFEM repository on the Sourceforge platform [1]. xx16 contains instructions to evaluate a range of implementation strategies as well as builtin timers and counters. The program outputs a high level report on the time spent in each major section of the program as well as an estimate the number of floating point operations per second. This research also made use of the Intel Vtune Amplifier XE performance monitoring software.

#### C. Porting

The ParaFEM software is built using a top level makefile that reads compiler specific flags from a machine specific include file. A new include file was written for the Intel compiler on the iDataplex system. Compared with using general purpose graphics processors, compiling for the Xeon Phi seems trivial. All that is needed to differentiate between compiling for a standard Xeon chip and the Xeon Phi is the addition of the compiler switch —*mmic* for the latter. The Xeon Phi runs its own installation of Linux locally, so an executable can be built to run on the card as easily as compiling for any other Linux system.

The Xeon Phi can be used in three different ways: (i) as a traditional accelerator, offloading computationally intensive instructions from the host to the Xeon Phi; (ii) as a standalone processor, running the executable entirely on the Xeon Phi or (iii) in mixed mode, as part of a heterogeneous system whereby the domain of a problem is subdivided over all available cores (in both the Xeon host and the Xeon Phi card). In this paper, the executable is run entirely on the Xeon host and entirely on the Xeon Phi card, enabling a direct comparison of the use of 2 x 12 Xeon processors and a single 60 core Xeon Phi card.

A number of different compiler options were evaluated and the best performance on the Xeon Phi was obtained using the following flags: -O3 -align array64byte and -opt-streaming-stores, the latter specifically to improve performance in memory bandwidth dominated programs. The sequential version of the Intel maths kernel library (MKL) was used for the matrix vector multiplication. The parallel version of MKL gave no benefit here because of the small size of the arrays.

#### D. Mixed Mode MPI/OpenMP

Previously unpublished work (carried out by MSc/PhD students at more than one research institution) has shown that the element by element preconditioned conjugate gradient (PCG) solver available in the ParaFEM library does not benefit from mixed mode MPI/OpenMP on standard x86 processors. The documentation available for the Xeon Phi [9] is very persuasive regarding how the hardware has been specially designed for threading on each physical core. So, despite a poor track record for mixed mode MPI/OpenMP, we were encouraged to consider this strategy again. OpenMP directives were inserted into the elements loop for testing.

The elements loop is parallelized using MPI, with each MPI process (or physical core) operating on its own local set

of finite elements. The mixed mode MPI/OpenMP code subdivides these local loops further, allowing us to test performance on up to 60 Xeon Phi cores with up to 4 threads per core, 240 way parallelism.

#### III. PRELIMINARY RESULTS

A number of different test runs have been carried out, but here we focus on the results of one specific finite element problem that best illustrates our preliminary findings. The analysis involves applying a vertical load to a patch on the surface of a cubic elastic domain; an engineering test problem described in the text book for use with program p121, a miniapp for the stress analysis of an elastic material [3]. In ParaFEM, there is a command line program called p12meshgen that can be used to quickly generate input decks of different sizes for this problem.

It should be noted that this section reports on the performance of a distributed do loop in the PCG solver that operates on a local set of finite elements assigned to each core. The results are representative of any general finite element analysis that uses the PCG solver, both from the point of view of the geometry of the model and the physics of the problem.

Every finite element stiffness matrix in the mesh is assumed to be unique, so each one has to be stored in memory. The "do loop" involves multiplying each stiffness matrix (here 60 by 60 double precision floating point numbers) by a vector. Relevant problems include those involving material or geometric nonlinearity (plasticity [10] and large deformations [7]); transient heat flow [4]; thermo-mechanical stress analysis [5] and forced vibrations [3].

The largest test problem (for the cubic domain) that could be stored in the 8GB memory of the Xeon Phi card, using this particular version of ParaFEM, was a mesh of 42,872 twenty noded hexahedral elements (521,780 equations to be solved).

#### A. Speed-up

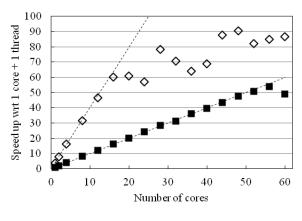

Fig. 1 shows speed-up for the largest test problem. The original MPI implementation (labeled 1 thread per core) scales linearly with increasing number of cores, with a slight drop off between 56 and 60 cores.

The speed up for 4 threads per core was calculated with respect to the time taken using 1 MPI core (with 1 thread). This helps highlight the advantage of the mixed mode MPI/OpenMP implementation. The mixed mode program shows a striking improvement in performance compared with the MPI only execution. On 1 to 16 cores, the use of 4 OpenMP threads per core leads to a "perfect" factor of 4 reduction in run time. Core counts greater than 16 cores do not continue this trend.

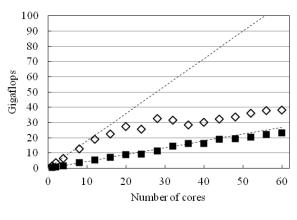

#### B. Percentage Peak Performance

The Xeon Phi used in this paper has a theoretical peak performance of 2 teraflops for single precision and 1 teraflop for double precision floating point operations. Here, the finite element mini-app has been compiled for computation using double precision. Fig. 2 shows that the (best to date) MPI implementation only achieves ~2.5% of peak performance

■1 thread per core ◇4 threads per core

Fig. 1. Speed-up using 1 thread and 4 threads per core

■1 thread per core ◇4 threads per core

Fig. 2. Operations per second using 1 thread and 4 threads per core

♦1 thread per core ■4 threads per core

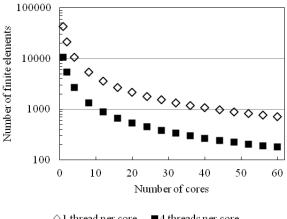

Fig. 3. Number of finite elements per thread

using 60 cores. In the mixed mode MPI/OpenMP case, there is a modest improvement to  $\sim 4\%$  peak using the maximum number of threads and cores, i.e. a maximum of 240 processes. The dotted line in Fig. 2 shows that if the 4 threads per core data series continued scaling linearly, this part of the mini-app could be expected to achieve a more respectable  $\sim 10\%$  peak performance.

#### C. Number of finite elements per thread

Fig. 3 shows the number of finite elements that each thread processes during the analysis. For the MPI only implementation (1 thread per core), performance scales linearly on up to 56 cores. This corresponds to ~765 elements per core. In the mixed mode MPI/OpenMP case, performance drops off markedly after 16 cores and 4 threads per core (64 threads), ~670 elements per thread. The number of elements reduces to ~178 elements per thread when the maximum 240 threads are used.

#### D. Comparison with the Xeon host

The best performing Xeon Phi implementation reported here runs around twice as fast as the 2 x 12 core Xeon processors on the host. At the moment, care needs to be taken in comparing the two platforms. There are further performance optimisations that can be implemented and tested on both.

#### IV. DISCUSSION

One of the key features of the finite element method is that it can be used to predict a range of physical processes occurring in domains of arbitrary geometry. In 3D, individual hexahedral or tetrahedral elements do not need to be perfect. They can be distorted so that a mesh can fill any space. As long as the elements have good aspect ratios, then the finite element method will give reasonable results.

The characteristics of a finite element, such as the shape and material properties, are captured in the element stiffness matrix. In any general problem, it is standard practice to create and store a unique element stiffness matrix for every element in the mesh. In this paper, our results indicate that, for the largest general problem that can be stored in 8GB RAM, there is not enough work to keep all the available hardware of the Xeon Phi busy.

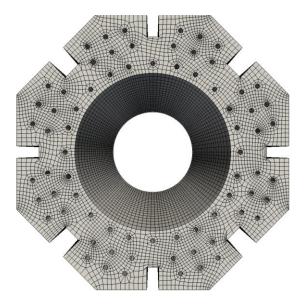

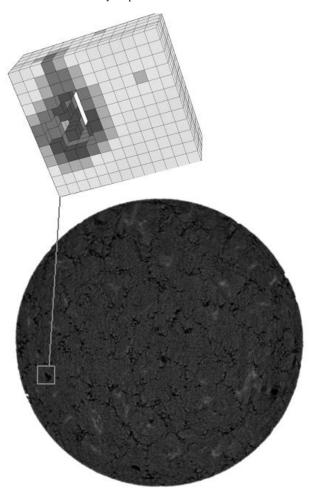

To address this problem, it is possible to reduce the storage requirements per element in certain problem specific cases. For example, when a mesh comprises identical elements, it is only necessary to store one stiffness matrix. In that case, the loop of matrix-vector computations can be replaced by a single matrix-matrix multiply. Typically meshes are not like this, as the nuclear model in Fig. 4 shows. This model has elements with different shapes on the face. Looking down the bore, each of the face elements sits on top of a column of identical elements. In this case, only elements on the top face need to be stored.

In some engineering problems, the stiffness elements are symmetrical, so only half needs to be stored. In the extreme case, when the elements are perfect hexahedra, some of the values in the symmetric part of the matrix are repeated.

Fig. 4. Finite element mesh of a nuclear graphite brick comprising arbitrarily shaped hexahedral elements.

Fig. 5. Slice through a typical X-ray tomography scan of nuclear graphite and voxel mesh based on patch of X-ray tomography data.

For example, the stiffness matrix storage for 8 node hexahedral elements derived from voxel-based meshes (Fig. 5) can be reduced from 24 x 24 floating point numbers to just 5. All the cases described have been coded in program xx16.

One final remark is that here, we advocate looking for ways of reducing the storage required by each finite element in order to deal with the difficulties that arise due to the small memory footprint per core (133MB) or per thread (33MB). The implication is that to achieve good performance, it may be better to have many "simple" low storage overhead finite elements in a mesh than a completely unstructured one where every element is unique. However, the story is not so simple. An area of active research in finite element analysis is the development of enriched elements to deal with special cases such as fracture; near incompressibility of the material or highly distorted elements [11]. These require an increased amount of storage and larger number of floating point operations per element. Getting the balance right, between computer performance and the accuracy of the engineering solution is therefore quite tricky!

#### **Acknowledgment**

This work was carried out in collaboration with the Intel Parallel Computing Centre hosted by The Hartree Centre, STFC Daresbury Laboratory Warrington, Cheshire, UK.

#### References

- [1] ParaFEM website, http://parafem.org.uk. Accessed 1 May 2016.

- [2] Message Passing Interface Forum, "MPI: A Message-Passing Interface Standard, Version 3.1, HLRS, 2015.

- [3] I.M. Smith, D.V. Griffiths and L. Margetts, "Programming the Finite Element Method", Wiley, 2014.

- [4] Ll.M. Evans, L. Margetts, V. Casalegno, L..M. Lever, J. Bushell, T. Lowe, A. Wallwork, P.G. Young, A. Lindemann, M.J.J. Schmidt and P.M. Mummery, "Transient thermal finite element analysis of CFC-Cu ITER monoblock using X-ray tomography data", Fusion Engineering and Design, 100, pp.100-111, 2015.

- [5] J.D. Arregui Mena, L. Margetts, D.V. Griffiths, L.M. Lever, G.N. Hall and P.M. Mummery, "Spatial variability in the coefficient of thermal expansion induces pre-service stresses in computer models of virgin Gilsocarbon bricks", J. of Nuclear Materials, 465, pp.793-804, 2015.

- [6] A. Shterenlikht and L. Margetts, "Three-dimensional cellular automata modelling of cleavage propagation across crystal boundaries in polycrystalline microstructures", Proceedings of the Royal Society A, Volume 471(2177), 2015.

- [7] F. Levrero, L. Margetts, E. Sales, S. Xie, K. Manda and P. Pankaj, "Evaluating the macroscopic yield behaviour of trabecular bone using a nonlinear homogenisation approach", Journal of the Mechanical Behaviour of Biomedical Materials, 61, pp. 384-396, 2016.

- [8] I.M. Smith and L. Margetts, "The convergence variability of parallel iterative solvers", Engineering Computations, 23(2), pp.154-165, 2006.

- [9] J. Reinders and J. Jeffers, "High Performance Parallelism Pearls: Volume 2", Elsevier, 2015.

- [10] I.M. Smith and L. Margetts, "Portable parallel processing for nonlinear problems", VII International Conference on Computational Plasticity, Barcelona, 2003.

- [11] T.H. Ong, C.E. Heaney, C.K. Lee, G.R. Liu, H. Nguyen-Xuan, "On stability, convergence and accuracy of bES-FEM and bFS-FEM for nearly incompressible elasticity", Computer Methods in Applied Mechanics and Engineering, 285, pp. 315-345, 2015.

# Evaluating the Maturity of OpenFOAM Simulations on GPGPU for Bio-fluid Applications

Ahmet Duran

Department of Mathematics

Istanbul Technical University (ITU)

Istanbul, Turkey

e-mail: aduran@itu.edu.tr

Senol Piskin

Department of Mechanical Engineering

Koc University

Istanbul, Turkey

Mehmet Tuncel

Department of Mathematics, ITU and

Informatics Institute, ITU

Istanbul, Turkey

#### Abstract

It is important to deal with the computational challenges for bio-medical fluid flow simulations and an *OpenFOAM* solver, *icoFoam*, for the large matrices coming from the simulation of blood flow in arteries on different HPC clusters. The flow problem produced various matrices as the time advances in simulation. In this study we examined the behaviour of the solvers for ill-conditioned matrices. We compared the CPU performance of the iterative solver *icoFoam* and the hybrid parallel codes (MPI+OpenMP) of a direct solver *SuperLU\_DIST 4.0* (see [2]) at TGCC Curie (a Tier-0 system) thin nodes at CEA, France (see [5]). Moreover, we compared the performance of the hybrid parallel codes of MPI+OpenMP+CUDA versus MPI+OpenMP implementation of *SuperLU\_DIST 4.0* at TGCC Curie (a Tier-0 system) hybrid nodes of CPU + GPU at CEA, France (see [5]). We discuss the performance, scalability and robustness of *OpenFOAM* on GPGPU cluster. We present our results regarding the speed-up of the solvers for the large matrices of size up to 20 million x 20 million. The authors thank to PRACE, GENCI and CEA for the opportunity to conduct our research in the frame of the Project 2010PA2505 awarded under the 18th Call for PRACE Preparatory Access.

#### I. INTRODUCTION

We investigated the challenges facing CFD solvers as applied to bio-medical fluid flow simulations and in particular the *OpenFOAM 2.1.1* solver, icoFoam, for the large pentadiagonal matrices coming from the simulation of blood flow in arteries with a structured mesh domain in PRACE-3IP project at TGCC Curie (a modern Tier-0 system) (see [1] and references therein). We generated a structured mesh by using blockMesh as a mesh generator tool. To decompose the generated mesh, we employed the decomposePar tool. After the decomposition, we used icoFoam as a flow simulator/solver tool. We achieved scaled speed-up for large matrices up to 64 million x 64 million matrices and speed-up up to 16384 cores on Curie thin nodes.

In this paper, we examined *OpenFOAM 2.2.2 "icoFoam"* simulator with an iterative solver such as diagonal incomplete LU preconditioned bi-conjugate gradient in addition to direct solvers such as distributed *SuperLU 4.0* (see [2]). The flow problem produced various matrices as the time advances in

simulation. The solution of the matrices obtained after each time step can be more challenging due to the changing structure of the matrices. This change may be caused by mess change or flow variable change. Generally the solution time of the matrices increases as the time advances in simulation.

It is challenging to discuss on the benefits or drawbacks of hybrid nodes. There are tradeoffs using GPU accelerators especially for the software packages or applications where it is not possible to fit the whole part into GPU. While it is expected to obtain a reduced time due to the accelerator, there would be communication over-head between the various processors and the GPU accelerators, as well. Therefore, it is important to obtain a feasible/optimal proportion of the tasks to MPI, OpenMP, and CUDA/OpenCL usages in emerging CPU+GPU systems. For example, it is not possible to do everything only in GPU for a complex algorithm like *SuperLU\_DIST*. Therefore hybrid nodes like Curie hybrid nodes at CEA in France provide opportunity.

It would be interesting to discuss about the relative energy requirements for thin nodes versus hybrid nodes. A diversification of hardware solutions based on the application capability may be needed in order to attain a good efficiency (see [6] and [7]). While the compute partition of Curie thin nodes having total of 80,640 cores consumes 2132 kW, the partition of Curie hybrid nodes having total of 288 Intel® + 288 Nvidia processors uses 108.80 kW as the total power (see TOP500 Supercomputing sites [8] and the Green500 List [9]). The partition of Curie hybrid nodes outperforms the Curie thin nodes when the energy efficiency is compared in terms of performance per watt and the rates of computation are 1,010.11 MFLOPS/W and 637.43 MFLOPS/W, respectively.

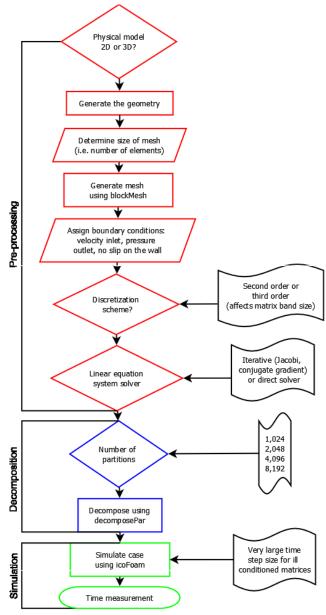

The remainder of this work is organised as follows: In Section 2, the test environment and the flow of approach are described. In Section 3, thin nodes results of the CPU performance for the iterative solver *icoFoam* and the hybrid parallel codes (MPI+OpenMP) of a direct solver SuperLU\_DIST 4.0 are compared. Moreover, simulation test results of hybrid node using MPI+OpenMP+CUDA versus MPI+OpenMP with *SuperLU\_DIST 4.0* solvers are presented. Section 4 concludes this work.

#### II. TEST ENVIRONMENT AND FLOW OF APPROACH

OpenFOAM (see [10]) is an open source Computational Fluid Dynamics (CFD) toolbox. It is a software package with many tools for several main tasks of the simulation such as preprocessing (meshing), decomposition and solution. Here, the solver refers to not only linear system solver but also Navier Stokes solver and simulator.

The first four matrices in Table 1 are obtained at time 0.00005 (s) of the simulation where the time step size is 0.00005 (s), as in [1]. Unlike [1], the last six matrices in Table 1 are encountered at the third time step, at time 0.012 (s) of the simulation where the time step size is 0.004 (s). This is a relatively large time step size for such a very small mesh size. Thus, we obtained challenging ill-conditioned matrices. Almost 5 or 7 banded sparse matrix occurs at each time step and the matrices are described in Table 1.

The flowchart in Figure 1 shows the flow of approach in the paper.

#### III. TEST RESULTS

The tests were done for only a few time steps due to time limitations, while the real case runs are conducted for more than thousands of time steps. No single CPU solution was possible because of long waiting times, so, information regarding the pre-processing (meshing), partitioning etc. are given for parallel processing. The most time consuming part of the simulation was the decomposing of the mesh. For 8192 partitions, it took over 3 hours. The "Simple" decomposition method was preferred since the running cases were for a structured mesh. This technique simply splits the geometry into pieces by direction, such as 32 pieces in x direction and 32 pieces in y direction. Since the mesh is structured, mC\_20M\_n matrix means 20M of cells in the fluid domain.

Figure 1. Flowchart for the flow of the approach including the main tasks

TABLE I. DESCRIPTION OF MATRICES

|            | N                                                  | NNZ        | NNZ/N           | Origin          |

|------------|----------------------------------------------------|------------|-----------------|-----------------|

| mC_8M      | 8,000,000 39,988,000 4.999 ITU Mathema             |            | ITU Mathematics |                 |

| mC_16M     | 16,000,000                                         | 79,984,000 | 4.999           | ITU Mathematics |

| mC_6M_D    | 6,000,000                                          | 41,800,000 | 6.967           | ITU Mathematics |

| mC_8M_D    | 8,000,000                                          | 55,760,000 | 6.970           | ITU Mathematics |

| mC_8M_n    | 8,000,000                                          | 39,988,000 | 4.999           | ITU Mathematics |

| mC_16M_n   | 16,000,000                                         | 79,984,000 | 4.999           | ITU Mathematics |

| mC_20M_n   | 20,000,000                                         | 99,982,000 | 4.999           | ITU Mathematics |

| mC_6M_n_D  | 6,000,000                                          | 41,780,000 | 6.963           | ITU Mathematics |

| mC_8M_n_D  | <b>M_n_D</b> 8,000,000 55,760,000 6.970 ITU Mathem |            | ITU Mathematics |                 |

| mC_10M_n_D | 10,000,000                                         | 69,660,000 | 6.966           | ITU Mathematics |

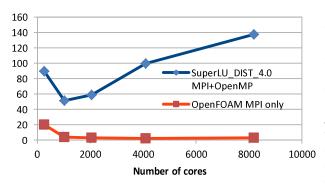

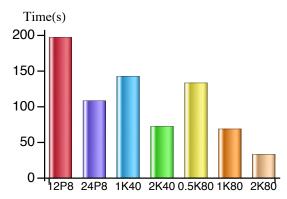

#### A. Thin Node Results

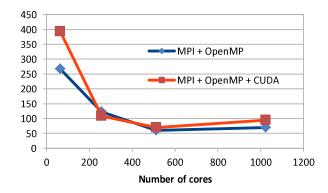

We compared the CPU performance of the iterative solver *icoFoam* and the hybrid parallel codes (MPI+OpenMP) of a direct solver SuperLU\_DIST 4.0 (see [2]) at TGCC Curie (a Tier-0 system) thin nodes at CEA, France (see [5]). Fig. 2 and Fig. 3 show the wall-clock time comparisons of the solvers, excluding the refinement time, for mC\_16M\_n and mC\_20M\_n on Curie thin nodes, respectively. The iterative solver with a diagonal incomplete LU preconditioned biconjugate gradient outperforms the direct solver *SuperLU DIST 4.0* for the simulation matrices.

Figure 2. Wall-clock time comparison of the solvers for mC\_16M\_n on Curie thin nodes

Figure 3. Wall-clock time comparison of the solvers for mC\_20M\_n on Curie thin nodes

#### B. Hybrid Node Results Using MPI+OpenMP+CUDA

TABLE II. THE CONFIGURATION OF MPI+OPENMP AND MPI+OPENMP+CUDA FOR THE DIRECT SOLVER

| Testbed:CURIE/              | hybrid | hybrid | hybrid | hybrid |

|-----------------------------|--------|--------|--------|--------|

| SuperLU_DIST version        | 4      | 4      | 4      | 4      |

| # of cores                  | 64     | 256    | 512    | 1024   |

| # of processes              | 16     | 64     | 128    | 256    |

| # of threads per<br>process | 4      | 4      | 4      | 4      |

| # of GPUs per<br>process    | 1      | 1      | 1      | 1      |

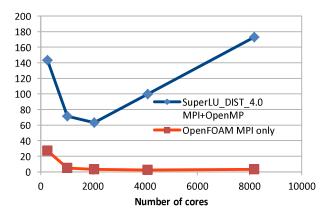

We compared the performance of the hybrid parallel codes of MPI+OpenMP+CUDA (see [4]) versus MPI+OpenMP implementation of SuperLU\_DIST 4.0 at TGCC Curie (a Tier-0 system) hybrid nodes of CPU + GPU at CEA, France (see [5]). Table 2 describes the corresponding configurations while we run the direct solver.

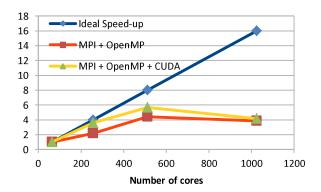

Table 3 shows the performance results for the ten simulation matrices described in Table 1. For example, Fig. 4 shows the comparison for the performances of MPI+OpenMP+CUDA and MPI+OpenMP implementations for mC\_20M\_n on Curie hybrid nodes. In Fig. 5, we observe a linear speed-up of the direct solver up to 512 cores for both implementations for mC\_20M\_n on Curie hybrid nodes.

Generally, we see that MPI+OpenMP implementation outperforms the hybrid of MPI+OpenMP+CUDA for this set of simulation matrices when we consider the wall clock times for the optimal number of cores because of several overheads coming from CUDA implementation for the direct solver algorithm. It is not possible to put everything only in GPU for SuperLU DIST. Therefore, the tasks should be proportioned to MPI, OpenMP, and CUDA/OpenCL. In SuperLU DIST 4.0 (see [4]), cuBLAS library execution is one of the most time consuming tasks performed in GPU in order to gain from explicit parallelization. On the other hand, there are overheads such as data transfer on PCIe between host and device memory (CPU and GPU) and new data structure changes related to data packing and scattering. Moreover, SuperLU is a complex algorithm and it is challenging to select the right combination for better intra-node communications and internode communications within CPU+GPU heterogeneous systems, under current technology limitations (see [3]).

The last eight matrices in Table 3 are challenging large matrices because they are relatively denser or ill-conditioned. The error labelled Error 1 occurs for small number of cores. We meet with an error message labelled Error 2 related to buffer size during the factorization subroutine pdgstrf, for the hepta-diagonal matrices. Error 3 is a CUDA stream error related to setting cuBLAS library execution stream.

Figure 4. Wall-clock time of direct solver for mC\_20M\_n on Curie hybrid nodes

Figure 5. Speed-up of direct solver for mC\_20M\_n on Curie hybrid nodes

TABLE III. WALL CLOCK TIMES (S) OF SUPERLU\_DIST 4.0 FOR THE LARGE PENTA-DIAGONAL MATRICES FOR 2D PROBLEMS AND HEPTA-DIAGONAL MATRICES FOR 3D PROBLEMS, DESCRIBED IN TABLE I, ON MPI+OPENMP VERSUS MPI+OPENMP+CUDA IMPLEMENTATIONS

| Matrices   | Number of cores        | 64      | 256     | 512     | 1024    |

|------------|------------------------|---------|---------|---------|---------|

|            | MPI + OpenMP           | 99.96   | 34.70   | 28.78   | 37.89   |

| mC_8M      | MPI + OpenMP +<br>CUDA | 94.70   | 39.10   | 43.70   | 60.72   |

|            | MPI + OpenMP           | 230.30  | 83.19   | 47.73   | 59.02   |

| mC_16M     | MPI + OpenMP +<br>CUDA | 236.83  | 87.23   | 60.00   | 81.41   |

|            | MPI + OpenMP           | Error 1 | 260.38  | 296.74  | 239.52  |

| mC_6M_D    | MPI + OpenMP +<br>CUDA | Error 1 | Error 2 | 254.44  | 257.15  |

|            | MPI + OpenMP           | Error 1 | 1005.96 | 516.86  | 387.20  |

| mC_8M_D    | MPI + OpenMP +<br>CUDA | Error 1 | 680.25  | Error 2 | 353.40  |

| G 03.5     | MPI + OpenMP           | 94.70   | 31.00   | 32.79   | 35.83   |

| mC_8M_n    | MPI + OpenMP +<br>CUDA | 70.94   | 38.27   | Error 3 | 61.34   |

|            | MPI + OpenMP           | 181.53  | 75.93   | 49.53   | 58.61   |

| mC_16M_n   | MPI + OpenMP +<br>CUDA | 233.22  | 75.58   | 61.42   | 83.61   |

| G 2035     | MPI + OpenMP           | 266.82  | 122.59  | 60.30   | 69.49   |

| mC_20M_n   | MPI + OpenMP +<br>CUDA | 393.49  | 108.90  | 69.60   | 94.99   |

|            | MPI + OpenMP           | 1178.51 | 409.15  | 248.84  | 211.70  |

| mC_6M_n_D  | MPI + OpenMP +<br>CUDA | 782.22  | 294.14  | Error 2 | 222.04  |

| G 034 5    | MPI + OpenMP           | Error 1 | 948.03  | 533.78  | 386.72  |

| mC_8M_n_D  | MPI + OpenMP +<br>CUDA | Error 1 | 682.02  | Error 2 | 349.16  |

| G 4034 ==  | MPI + OpenMP           | Error 1 | 877.92  | 465.60  | 373.09  |

| mC_10M_n_D | MPI + OpenMP +<br>CUDA | Error 1 | 752.78  | Error 2 | Error 3 |

#### IV. CONCLUSION

We performed bio-medical fluid flow simulations for the large matrices coming from the simulation of blood flow in arteries in emerging CPU+GPU systems. The flow problem produced various challenging matrices during the simulation. We compared the CPU performance of the iterative solver icoFoam and the hybrid parallel codes (MPI+OpenMP) of a direct solver SuperLU DIST 4.0 (see [2]) at TGCC Curie (a Tier-0 system) thin nodes at CEA, France (see [5]). We observe that the iterative solver with a diagonal incomplete LU preconditioned bi-conjugate gradient outperforms the direct solver SuperLU DIST 4.0 for the simulation matrices. Moreover, we compared the performance of the hybrid of MPI+OpenMP+CUDA parallel codes versus MPI+OpenMP implementation of SuperLU DIST 4.0 at TGCC Curie (a Tier-0 system) hybrid nodes of CPU + GPU at CEA, France (see [5]). Generally, we notice that MPI+OpenMP implementation outperforms the hybrid of MPI+OpenMP+CUDA for the set of simulation matrices when we consider the wall clock times for the optimal number of cores because of several overheads coming from CUDA implementation for the complex direct solver algorithm. Furthermore, we met with several errors for the challenging simulation matrices. We believe that the technology developments in emerging CPU+GPU systems will increase the scalability of related complex algorithms by eliminating the bottlenecks coming from communication and right matching of system components required for special applications.

#### ACKNOWLEDGEMENT

This research was supported by the Project 2010PA2505 awarded under the 18th Call for PRACE Preparatory Access and we acknowledge that the results of this research have been achieved using the PRACE Research Infrastructure resource TGCC Curie (a modern Tier-0 system) based at CEA in France.

#### REFERENCES

- [1] A. Duran, M.S. Celebi, S. Piskin, and M. Tuncel, "Scalability of OpenFOAM for bio-medical flow simulations," Journal of Supercomputing, 71(3), 2015, pp. 938-951.

- [2] X. S. Li, J. W. Demmel, J. R. Gilbert, L. Grigori, M. Shao, and I. Yamazaki, SuperLU Users' Guide, Tech. Report UCB, Computer Science Division, University of California, Berkeley, CA, 1999, update: 2011

- [3] M.S. Celebi, A. Duran, M. Tuncel and B. Akaydın, Scalable and improved SuperLU on GPU for heterogeneous systems, *PRACE* (Partnership for Advanced Computing in Europe), PRACE PN: 283493, *PRACE-2IP white paper, Libraries*, WP 44, July 13, 2012.

- [4] P. Sao, R. Vuduc, and X.S. Li, "A distributed CPU-GPU sparse direct solver," Euro-Par 2014 Parallel Processing, Lecture Notes in Computer Science vol. 8632, 2014, pp. 487-498.

- [5] http://www-hpc.cea.fr/en/complexe/tgcc-curie.htm.

- [6] N. Meyer, M. Lawenda, et al., Best Practices for HPC Procurement and Infrastructure, PRACE-2IP project, under Grant agreement No. RI-283493, Aug. 2013.

- [7] J. David, JN Richet, E. Boyer, N. Anastopoulos, G Collet, GC Verdiere, et al., Best Practice Guide Curie v1.17, PRACE, Nov. 2013.

- [8] TOP500 Supercomputing sites, http://top500.org/

- [9] The Green500 List, http://www.green500.org

- [10] OpenFOAM main site. http://www.openfoam.com

### Code modernization of DL\_MESO LBE to achieve good performance on the Intel Xeon Phi.

Sergi Siso and Luke Mason

Intel Parallel Computing Centre, Hartree Centre

Science and Technology Facilities Council

Daresbury, United Kingdom

sergi.siso@stfc.ac.uk, luke.mason@stfc.ac.uk

#### Michael Seaton

Computational Chemistry Group Science and Technology Facilities Council Daresbury, United Kingdom michael.seaton@stfc.ac.uk

#### Abstract

The Lattice Boltzmann Equations of DL\_MESO have been re-implemented using a Two-Grid algorithm, threaded programming and vectorization in order to effectively utilize novel highly parallel architectures such as the one offered by the Intel Xeon Phi.

#### I. INTRODUCTION

DL\_MESO LBE [1][2] is a general purpose mesoscopic simulation package which can simulate multi component lattice-gas systems using the Lattice Boltzmann Equation (LBE). It is used to model systems with multiple fluids and/or phases coupled to solute diffusion and heat transfer, as well as apply geometrically complex boundaries comparatively easily.

The main version of this code implements a SWAP algorithm [3], where data dependencies are circumvented by a strict processing order of the lattice nodes. The SWAP algorithm performs well using multiple low core count processors with MPI, however, performance in a modern architecture like the Intel Xeon Phi was disappointing.

In this work we have re-implemented the Lattice Boltzmann solver within DL\_MESO using OpenMP threads and SIMD clauses and a double-buffered and computationally simpler algorithm. This implementation utilises twice as much memory but shows better performance (x5 on Xeon Phi and x1.7 in Xeon processors) and scalability characteristics. The new implementation has the advantage of being ready to use the features of other modern and future hardware architectures to come.

This paper starts describing the Xeon Phi architecture in section 2 and the DL\_MESO Lattice Boltzmann physics in section 3. Then, it explains the SWAP algorithm implementation used in the original DL\_MESO package, section 4, and the Two Grid implementation we have implemented for the new version of the code, section 5. Finally section 6 gives details of the vectorization while section 7 compares the performance and scalability of the two versions of the code.

#### II. INTEL XEON PHI

The target architecture for this project is the Intel Xeon Phi Knights Corner coprocessor. The Xeon Phi is a highly parallel architecture which consists of many small, power efficient, inorder cores, each of which has a 512-bit vector processing unit (SIMD unit) [4]. It is a x86 64bits architecture with a cache memory system similar to general purpose CPUs, therefore legacy x86 codes that use to run well on CPUs also run on the Xeon Phi, but due to its large number of threads and vector units length, it is challenging to port existing applications to this platform. Nevertheless, given the trends seen in CPU design in the recent years, porting applications to the Xeon Phi helps to prepare the applications to future generations of hardware.

Specifically, the results presented in this paper are obtained using the Intel Xeon Phi Coprocessor 5110P with the following specifications:

- 60 cores, 240 threads (4 threads/core)

- 1.053 GHz,

- 1 TeraFLOP double precision theoretical peak performance,

- 8 GB memory with 320 GB/s bandwidth,

- 512 bit wide SIMD vector engine,

- 32KB L1, 512KB L2 cache per core,

- Fused multiply-add (FMA) support.

The performance is compared with a compute node using two Intel Ivy Bridge Xeon E5-2697 v2 at 2.70GHz [5].

#### III. LATTICE BOLTZMANN METHOD AND DL MESO

DL\_MESO is a C++ general purpose mesoscopic simulation package which comes with two different simulation methods: Dissipative Particle Dynamics (DPD) and Lattice Boltzmann equations (LBE) [1][2]. The current work is concerned with the LBE method exclusively.

The LBE is a computational fluid dynamics method which has emerged from the lattice-gas automata and is used to simulate a multitude of flow problems. In LBE a fluid can be represented by using the probability of finding one of its particles at a given position in space and time with a given momentum, described by a density distribution function,  $f(\vec{x}, \vec{p}, t)$ , depending on the position,  $\vec{x}$ , the momentum,  $\vec{p}$  and time, t. Over a single time-step  $\Delta t$  the distribution function at each lattice point  $\vec{x}$  evolves initially by collisions

$$f_i(\vec{x}, t^+) = f_i(\vec{x}, t) + C_i$$

(1)

and then by propagation between neighbouring lattice sites

$$f_i(\vec{x} + \vec{e}_i \Delta t, t + \Delta t) = f_i(\vec{x}, t^+)$$

(2)

where  $\vec{e_i}$  is the velocity vector for lattice link  $(\vec{\iota}, t^+)$  denotes a time during the time-step after collisions have taken place and  $C_i$  is a collision operator acting on deviations from local equilibria.

DL\_MESO implements several choices for collision the variable. The work presented in this paper we have used the single relaxation step Bhatnagar-Gross-Krook (BGK) [5]

$$C_i = -\frac{f_i - f_i^{eq}}{\tau} \tag{3}$$

with a relaxation time  $\tau$  related to the kinematic viscosity of the fluid  $\nu$ . The distribution function at local equilibrium for a particular point can be determined from its density and velocity

$$f_i^{eq} = \rho w_i \left[ 1 + 3(\overrightarrow{e_i} \cdot \overrightarrow{u}) + \frac{9}{2} (\overrightarrow{e_i} \cdot \overrightarrow{u})^2 - \frac{3}{2} \overrightarrow{u}^2 \right]$$

(4)

The relaxation time is determined by

$$v = c_s^2 \left(\tau - \frac{1}{2}\right) \Delta t \leftrightarrow \tau = \frac{v}{c_s^2 \Delta t} + \frac{1}{2}$$

(5)

where  $c_s$  is the speed of sound for the lattice in use: this value is equal to  $\Delta \vec{x}/(\sqrt{3}\Delta t)$  for square lattices following the D3Q19 form.

To deal with interactions between multiple phases and fluid species the Shan-Chen algorithm [9][10] is used in this work (DL\_MESO has more options), which gives the force on fluid a as

$$F_a = -\psi_a(x) \sum_b g_{ab} \sum_i w_i \psi_b(\vec{x} + \vec{e_i}) \vec{e_i}$$

(6)

$g_{ab}$  is the interaction coefficient between species a and b, which can be related directly to the interfacial tension between the species  $\sigma_{ab}$ , and  $\psi_a$  is a pseudo-potential for species a, related to the fluid density of that species.

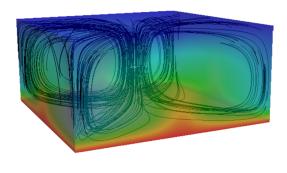

The advantage of DL\_MESO over other packages implementing the Lattice Boltzmann equation is that it allows computing multiple components and/or fluid phases and coupling them with other physics like the heat transfer function or solute diffusion equations. This flexibility to plug in different physics makes DL\_MESO LBE ideal to simulate applications such as the cavity flow problem [13], or subjecting an initially stationary fluid to a temperature difference between two solid boundaries [14], shown at figure 1.

Figure 1. Rayleigh-Benard natural thermal convection of fluid between cold and hot plates.

The Lattice Boltzmann method is generally suitable for parallel computing and it is easy to code, however, the mentioned flexibility in the physics comes with some performance constraints. The necessity of computing the pseudo-potentials in each time step and therefore having non-local collision computations complicates the algorithm compared to other LBE implementations.

#### IV. SWAP ALGORITHM

There exist several algorithms to implement the Lattice Boltzmann equations and each of them offers different trade-offs in terms of memory utilization and performance [8]. Originally, DL\_MESO LBE was implemented using a SWAP algorithm [3] with the MPI parallel programming model. In SWAP algorithm the data dependencies on the grid are avoided by a strict processing order of the lattice nodes and by

explicitly exchanging some of the distribution values of the lattice node at hand with those of neighbouring nodes.

Because it removes the data dependencies, it requires only one lattice to store the state of the simulation during the runtime. Hence, it is very efficient in terms of the total memory we need to allocate for a given problem size.

However, the SWAP algorithm is challenging to implement in highly parallel architectures due to the strict order of processing of the different lattices. For instance, we need to ensure that each lattice of a neighbour particle has computed its collision before we swap them. In the original implementation of the code this involves five different loops, all going through the whole data-structure. This effectively creates multiple parallel barriers in each iteration and the cache utilization is poor. The vectorization of the arithmetic operations is also challenging because the inner loop has small trip counts and often we need to introduce peeling and remainder loops to accommodate the size of the loop to the vector registers.

Table 1 shows the routines of the original DL\_MESO code where most execution time is spent in an execution on a Xeon processor, together with the L1, L3 and DRAM and the percentage of Floating Point operations performed at the vector units on that execution. This data was obtained using the Intel VTune Performance analysis tool [11].

| Function                    | Time<br>(%) | L1<br>Bound | L3<br>Bound | DRAM<br>Bound | Vect<br>FP<br>(%) |

|-----------------------------|-------------|-------------|-------------|---------------|-------------------|

| fGetSpeedShanChe.           | 13.0        | 0.299       | -           | -             | 0                 |

| fSwapPair <double></double> | 12.0        | 0.697       | 0.076       | 0.892         | 0                 |

| MPID_nem_sshm               | 10.2        | 0.425       | 0.033       | 0             | 0                 |

| fGetAllMassSite             | 7.40        | 0.241       | 0.504       | 0             | 100               |

| fCalcInteraction Sh.        | 7.00        | 0.151       | 0.007       | 0.04          | 60                |

| fGetEquilibriumF            | 6.80        | 0.318       | 0.009       | 0             | 55                |

Table 1. Performance metrics of DL\_MESO LBE SWAP implementation.

#### V. Two-Grid Algorithm

The Two-Grid Algorithm implemented in DL\_MESO in the current work is a simpler approach. The probability function distributions are stored in two different grids, A and B. The pseudo-potentials and the collisions are performed with the values of the grid A and the post-collision values of each node are immediately streamed to their neighbours and stored in lattice B. At the end of the iteration lattice pointers to A and B are swapped and the iteration starts over

Although the Two-Grid Algorithm is not as sophisticated as the SWAP algorithm, it does not have compute order dependencies and allows a more natural parallel implementation from both: threads and vector instructions.

DL\_MESO used the OpenMP capabilities to distribute the work between different threads using a static schedule and among the vector lanes using the SIMD directive available since OpenMP 4.0 [12]. Hence, the parallel implementation is just a few additional lines to the serial implementation of the code. This greatly reduces the complexity of the code because both implementations share the same code base.

The new code has the main advantage that the algorithm loops can be fused into just two, one for the pseudo-potentials pre-computations and another for the collision and streaming steps. Consequently, the data-structure is only traversed twice and each element that is reads has more computational steps to be done. This leads to a lower cache pressure as shown in Table 2. The table presents main function in the Two-Grid version of the code, again with the L1, L3, DRAM and vectorization usage provided by VTune.

| Function           | Time<br>(%) | L1<br>Bound | L3<br>Bound | DRAM<br>Bound | Vect<br>FP<br>(%) |

|--------------------|-------------|-------------|-------------|---------------|-------------------|

| solve_x_iterations | 66.2        | 0.54        | 0.004       | 0.234         | 100               |

Table 2. Performance metrics of DL\_MESO LBE Two-Grid implementation.

#### VI. VECTORIZATION AND COMPILE TIME PARAMETERS

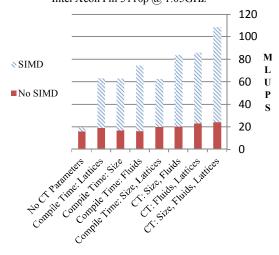

To get a good performance from the explicit vectorization implementation we rely in the ability of the compiler to unroll some loops. Specifically, we want to unroll the two most inner loops in order to vectorise the 3rd nested loop, which has a considerably larger trip count. However, the compiler does not have enough information during compile time to properly execute such decisions. Therefore, our solution is to provide some of the simulation parameters at the compiling stage enabling the compiler to take smarter decisions.

#### Adding Compile Time Parameters Intel Xeon Phi 5110p @ 1.05GHz

Figure 2. MLUPS of DL\_MESO LBE simulation with different parameter set up at compile time.

Figure 2 presents the Million Lattice Update Per Second (MLUPS) for several combinations of parameters defined at compile time. The figure demonstrates that when we provide more parameters the compiler is able to produce significantly better vectorization of the code, and that leads to faster iterations.

#### VII. PERFORMANCE AND SCALABILITY COMPARISON

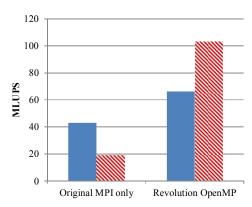

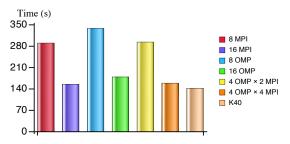

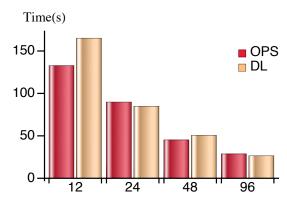

Figure 3 shows how the performance on the Intel Xeon Phi is improved by more than five times with the new implementation compared to the SWAP algorithm. The performance on the Xeon processors is also improved by 1.5.

Considering the new performance executing a simulation on the Intel Xeon Phi is 70% faster than in a 2 by 12 core Xeon node. Also, this new implementation has the advantage of being ready to use the features of future hardware architectures where longer vector units and more cores are expected.

#### DL\_MESO LBE Performance

(BGK Shan Chen with 4 fluids, Size: 160<sup>3</sup>)

2 x Intel Xeon E5-2697 v2 (24 tasks or threads)

Name Intel Xeon Phi 5110p (240 tasks or threads)

Figure 3. Performance comparison of the SWAP and Two-Grid algorithm in the Xeon and the Xeon Phi processors.

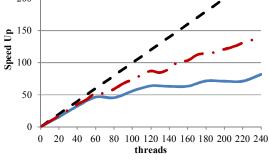

Figure 4 plots the scalability of both implementations in the Xeon Phi architecture. Note that the SWAP algorithm was implemented using MPI programming model while the Two-Grid algorithm is implemented using the OpenMP API for threaded programming. In both cases they scale reasonably well until 60 cores, one thread per core in the Xeon Phi 5110P, but after 60 cores the Two-Grid OpenMP version scales better by reaching x140 speed up at 240 threads while the SWAP implementation reaches 81 at 240 MPI processes.

#### REFERENCES

- M. A. Seaton, R. L. Anderson, S. Metz and W. Smith, DL\_MESO: highly scalable mesoscale simulations, Mol. Sim. 39 (10), 796–821 (2013)

- [2] M. A. Seaton and W. Smith, DL\_MESO User Manual

- [3] K. Mattilaa, J. Hyväluomab, T. Rossia, M. Aspnäsc and J. Westerholme, An efficient swap algorithm for the lattice Boltzmann method, Computer Physics Communications. February 2007

- [4] Intel Corporation, Intel Xeon Phi Coprocessor System Software Developers Guide, 2012, http://software.intel.com/en-us/mic-developer.

- [5] Intel® Xeon® Processor E5-2600 v2 Product Family. http://ark.intel.com/products/series/75291/Intel-Xeon-Processor-E5-2600-v2-Product-Family#@All

- [6] J. Latt, How to implement your DdQq dynamics with only q variables per node (instead of 2q), Technical Report, Tufts University, Medford, USA, 2007

#### DL\_MESO LBE Scalability

(BGK Shan Chen with 4 fluids, Size: 160<sup>3</sup>)

Original SWAP algorithm with MPI

Two-Step Two-Grid Algorithm with OpenMP

200

Figure 4. Parallel scalability comparison of the SWAP algorithm (MPI) and the Two-Grid algorithm (OpenMP) on the Intel Xeon Phi.

- [7] P.L. Bhatnagar, E.P. Gross, M. Krook, A model for collision processes in gases. I. Small amplitude processes in charged and neutral one-component systems, Phys. Rev. 94 (3) (1954) 511– 525.

- [8] M. Wittmanna, T. Zeisera, G. Hagera, G. Welleinb. Comparison of different Propagation Steps for the Lattice Boltzmann Method, Computers and Mathematics with Applications

- [9] X. Shan and H. Chen. Lattice Boltzmann model for simulating ows with multiple phases and components. Physical Review E: Statistical Physics, Plasmas, Fluids, and related interdisciplinary topics, 47(3):1815{1819, March 1993.

- [10] X. Shan and H. Chen. Simulation of nonideal gases and liquidgas phase transitions by the lattice Boltzmann equation. Physical Review E: Statistical Physics, Plasmas, Fluids, and related interdisciplinary topics, 49(4):2941 (2948, April 1994.

- [11] Intel® VTune™ Amplifier 2016. https://software.intel.com/en-us/intel-vtune-amplifier-xe

- [12] OpenMP Application Program Interface Version 4.0 July 2013

- [13] S. Hou, Q. Zou, S. Chen, G. Doolen, and A.C. Cogley, Simulation of cavity flow by the lattice Boltzmann method, J. Comp. Phys. 118 (1995), pp. 329-347.

- [14] Z. Guo, B. Shi, and C. Zheng, A coupled lattice BGK model for the Boussinesq equations, Int. J. Numer. Meth. Fl.39 (2002), pp. 325-342.

# Back to the Future? High Performance Computing and ARM

Chris Adeniyi-Jones, ARM Research Cambridge, United Kingdom

Abstract—Achieving Exascale levels of performance for HPC systems within a sustainable power budget is the widely held goal for many. Improving the efficiency of HPC systems is going to require novel technologies and new ways of using existing technology. ARM is a leading provider of Intellectual Property. Our range of IP products and our partnership business model enables our partners to address many different markets. I will highlight the Mont-Blanc project as an example of a different approach to HPC; what was done and what we learnt. I will also discuss the changes over the past five years and how new products are helping us prepare for the next five years of advances in high-performance computing.

# Low-Power, Fault-Resilient Communications in a Million-Core Neural Processing Architecture

Javier Navaridas, Mikel Luján, Luis A. Plana and Steve B. Furber School of Computer Science, The University of Manchester Oxford Road, Manchester, UK, M13 9PL

Abstract— The SpiNNaker neuromimetic architecture is a biologically-inspired massively-parallel architecture based on a custom-made multicore System-on-Chip (SoC). In order to deal with the challenging and atypical communication demands of spiking neural networks, SpiNNaker features a specialised, ad hoc communication infrastructure based around a custom-made multicast router. This paper summarizes the main research work around the peculiarities of SpiNNaker's architecture and interconnects focusing on the most exceptional features of the platform. We derived the main topological properties of the network, analyzed the effects of failures congestion and traffic burstiness in the stability of the interconnect and, finally, proposed a collection of multicast routing algorithms.

Keywords—Interconnection Networks, Massively Parallel Systems, Multicast Routing Algorithms, Performance Evaluation.

#### I. INTRODUCTION

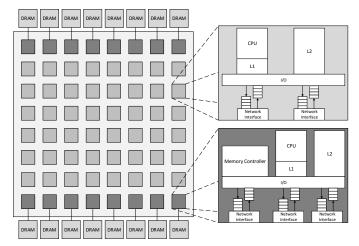

SpiNNaker is a bespoke massively-parallel architecture targeting the simulation, in biological real-time, of very largescale spiking neural networks, with more than 10<sup>9</sup> neurons. To put this number in context, it roughly represents 10% of the human cortex. Spiking neural networks communicate by means of spike events which occur when a neuron is stimulated beyond a given threshold and discharges an electrical impulse. These spikes are communicated to all connected neurons, with typical fan-outs of the order of 10<sup>3</sup>. At a realistic biological firing rate of 10Hz, there could be more than 10<sup>10</sup> neuron firings per second, which can replicate up to 10<sup>13</sup> communication events per second in the largest SpiNNaker configuration. Thus, an essential problem inherent to the simulation of spiking neural networks is how to distribute large numbers of small packets very widely amongst up to the million processors featured by SpiNNaker in an efficient way and with minimal latency. In this paper, we discuss the most important research that has been carried out around the custommade interconnection network of SpiNNaker. In [1], we performed a theoretical analysis of the network, deriving theoretical properties such as the maximum throughput and distance-related characteristics of its topology. We also studied the fault tolerance capabilities of the system showing that the network is able to adapt and to remain stable in the presence of failures [3]. Later on, we investigated how the traffic burstiness inherent to the application affects network stability. As increasingly larger configurations of the system have become available, there has been a great effort on understanding how to better exploit SpiNNaker's multicast infrastructure [4, 5] in order to prevent the interconnection network from becoming the main performance and scalability bottleneck.

#### A. Machine Construction Progress

The construction of large-scale versions of SpiNNaker is ongoing and is expected to culminate with the million-core system in the following months. Some prototypes and production systems have already been designed and fabricated. Back in 2010 a first batch of test chips (two cores and a fully functional router) were produced and successfully demonstrated running spiking neural nets. This was followed in 2011 by the production of small quantities of full-fledged SpiNNaker chips with 18 ARM cores and the development of small boards, able to house four SpiNNaker chips and to support inter-board communications. These boards, due to their low-power design, have been used as control devices for robotic systems. As shown in Fig. 1, we have reached most milestones in the path towards the full-fledged SpiNNaker: a 48-chip board has been designed and large numbers of them have been produced and can be interconnected to construct increasingly large machines. One board forms a 10<sup>3</sup>-core machine, one rack frame with 24 boards forms the 10<sup>4</sup> one, a cabinet with five of these frames (120 boards) forms the 10<sup>5</sup> machine. Very recently 5 of these cabinets have been installed. The final expansion to reach the full-fledged, million-core SpiNNaker machine will be to add 5 more cabinets together, which will be done in the next few months.

#### B. System software and libraries

Aside from the hardware, an extensive collection of system software and application libraries is already offered to operate SpiNNaker and new features are developed and released frequently. Among all the software involved in SpiNNaker, is especially important the PyNN frontend, a domain specific language devised to define spiking neural networks widely used within the neuroscientist community. The PyNN/SpiNNaker combination exploits the system flexibility and decouples neural applications from the actual hardware, allowing users to rapidly develop and simulate spiking neural networks without any knowledge of the intricacies of the underlying system. Thanks to this transparency for the enduser, the adoption of SpiNNaker as a simulation platform is rapidly growing within the cognitive computing community.

#### II. SPINNAKER ARCHITECTURE

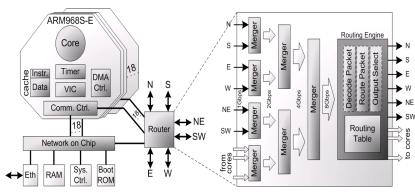

The main foundations of SpiNNaker's design philosophy were to reduce power consumption, to improve reliability by means of high redundancy and to provide a flexible architecture, general enough to run a wide range of applications. Each SpiNNaker SoC contains 18 low-power

a) Unpackaged (left) and

b) 48-chip production board (10<sup>3</sup> machine)

c) 24-board frame (10<sup>4</sup> machine)

d) 19" rack cabinets (halfway to 106 machine)

Fig. 1. Different sizes of SpiNNaker Machines, from a single chip to the recently installed 5-cabinet system.

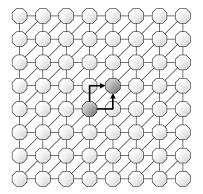

general-purpose ARM968 cores, typically running an independent event-driven process, which responds to events by different on-chip modules: communications controller and DMA controller, among others. The chip is packaged together with a 128 MB SDRAM, whose primary function is to store synaptic information. The chips are interconnected (see Fig. 2) using a two-dimensional triangular torus relying on a custom-made on-chip multicast router which handles both inter- and intra-chip communications. It has 18 ports for the cores plus six external ports to communicate with adjacent chips. To avoid the high complexity intrinsic to crossbar-based designs, the SpiNNaker router uses a simpler architecture in which ports are hierarchically merged into a single pipelined queue so that only one packet can use the routing engine at once. The routing engine is not expected to become a bottleneck as it has much higher bandwidth than the transmission ports (8 Gbps vs. 250 Mbps). The router supports point-to-point and multicast communications using small packets of 40 bits. The multicast engine reduces the pressure at the injection ports and the number of packets traversing the network and so is the main communication method during regular operation of the system.

Another interesting aspect of the interconnection architecture is the routing paradigm. Following the Address

Event Representation protocol, packets do not contain any information about their destination(s), only an identifier of the neuron that has fired. The information necessary to deliver a neural packet to all the relevant cores and chips is compressed and distributed across the 1024-word routing table within each router. To minimize the impact of such an exiguous resource and allow the system to perform complex routing, routing tables offer a masked associative route look-up and routers are designed to perform a default routing—which requires no entry in the routing table—by sending the packet to the port opposite to the one the packet comes from, i.e. if a packet comes from the North it will be sent to the South. Routing tables are not intended to remain static during long simulations. They can be modified dynamically in real-time to accommodate scenarios of congestion or even failures in the interconnection network.

The flow-control is very simple: when a packet arrives to the routing engine, one or more output ports are selected and the router tries to transmit the packet through them. If the packet cannot be forwarded, the router will keep trying, and after a given period of time it will also test the clockwise emergency route. Finally, if a packet stays in the router for longer than a given threshold the packet will be dropped to avoid deadlock. This threshold is an arbitrary router configuration parameter which was thoroughly studied in [1].

Fig. 2. Example of an 8×8 SpiNNaker topology (left) and a communication-centric diagram with the main components of a chip (right). The peripheral connections of the topology are not depicted for the sake of clarity. The regular route (slashed line) and the two emergency routes (thick arrows) between the shaded nodes are shown.

#### III. EVALUATING THE INTERCONNECTION NETWORK

#### A. Topological Analysis

One of the most important aspects of a network is its topology as it has a great effect on the overall performance both in terms of bandwidth and latency. As a first step to assess SpiNNaker network [1], we derived theoretical properties such as the maximum throughput  $(\Theta)$ , the average distance  $(\delta)$  and the diameter (D) based on the nodes per dimension (n):

$$\Theta = \frac{16 \cdot n}{n^2} = \frac{16}{n} packets/cycle/node$$

(1)

$$D = \frac{n}{2} + \left| \frac{n}{6} \right| = \left| \frac{2 \cdot n}{3} \right| \tag{2}$$

$$\delta = \frac{\sum_{i=1}^{\frac{n}{2}} \left(6 \cdot i^2\right) - 3 \cdot \frac{n}{2} + \sum_{i=1}^{\left\lfloor \frac{n}{6} \right\rfloor} 2 \cdot \left(\frac{n}{2} + i\right) \cdot \max\left(1, 9 \cdot \left(\left\lfloor \frac{n}{6} \right\rfloor - i\right) + 3 \cdot \left(\frac{n}{2} \bmod 3\right)\right)}{n \cdot (n-1)}$$

(3)

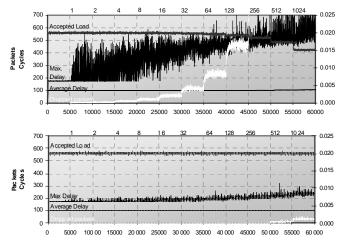

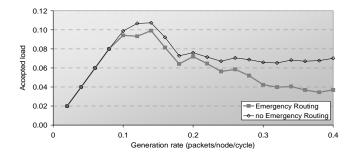

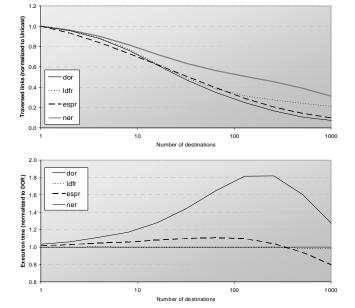

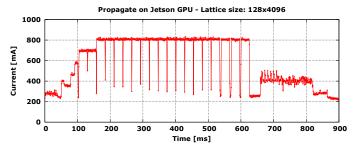

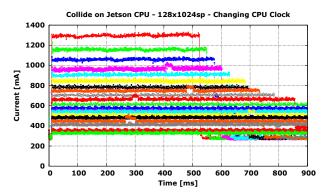

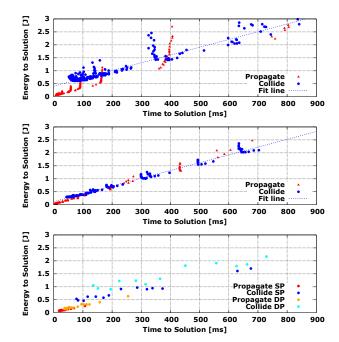

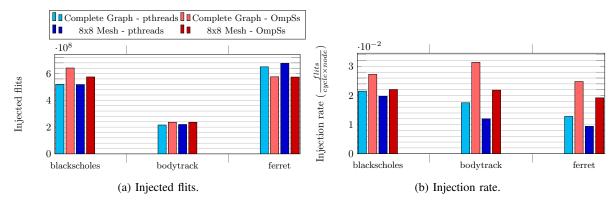

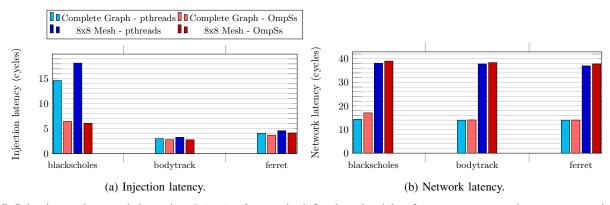

#### B. Network stability under failures

Another interesting insight coming from our previous evaluations is the stability of SpiNNaker's interconnect in the presence of failures thanks to the emergency routing mechanism [1]. Fig. 3 shows the temporal evaluation of a SpiNNaker system when the emergency routing is either deactivated or activated. In these simulation results, we started with a fault-free network and every 5k cycles the number of faults is increased (to 1, 2, 4, 8, etc as per the top axis). These results show clearly that whereas performance metrics in the system without Emergency routing have large fluctuations as failures are added up, the system with emergency routing shows a very stable operation with small variations in max latency as we approach large number of failures. However, while the emergency routing mechanism is shown to be excellent when dealing with failures, it has been found more recently to be one of the contributors of the system vulnerability to congestion. Fig. 4 shows the network throughput as measured with and without the mechanism activated. It is clear that activating this mechanism may be counterproductive in scenarios of congestion (after about 0.1 load) because accepted load is reduced when the emergency

Fig. 3 Temporal evolution of the systems under uniform traffic at a given load of 0.02 packets/node/cycle. Without emergency routing (top) and with emergency routing (bottom). *Adapted from [2]*.

Fig. 4 Effects of emergency routing mechanism on network throughput.

routing is used. Although congestion is not expected to be a major problem in SpiNNaker given the small packet size and the traffic locality, the emergency routing mechanism is normally deactivated unless failures are detected in order to avoid network reaching saturation prematurely.

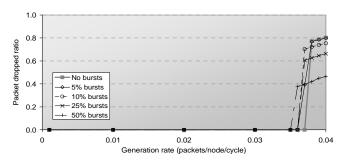

#### C. Effects of traffic burstiness

SpiNNaker features a very distinctive execution model which generates traffic with some characteristics which are dissimilar from the typical workloads that can be found in other parallel computers such as datacentres or HPC systems. For this reason we later investigated the effects that these characteristics (traffic burstiness, locality and causality) had on the network [3]. The most important of these characteristics is, without any doubt, that the event-driven nature of the application tends to generate traffic in bursts because all the neural activity is checked at the beginning of each simulation step (typically with a resolution of 1 ms). Fig. 5 shows the effect that increasing the burstiness of the traffic – up to 50% of the traffic being in the form of 10-packet bursts – has on the packet dropped ratio of the system. It can be seen that the proportion of bursts barely affects the generation rate when the network starts dropping packets, just about a 5% earlier when half of the traffic is bursty. Note that this experiment was carried out in an extremely pessimistic configuration in which the traffic was mostly non-local and the injection rates in which packets are first dropped are about 4 times higher than the typical operation of the system. These results show that SpiNNaker will be able to perform in a stable manner when dealing with the anticipated network workloads.

#### D. Multicast Routing

With the relentless increase in the size of the available systems the use of SpiNNaker's multicast infrastructure is becoming increasingly important [4, 5] as route generation has

Fig. 5 Effects of burst in the packet dropped ratio. Bursts of 10 packets, Adapted from [3].

a) Dimension Order Routing (DOR) b) Longest Dimension First Routing (LDFR) c) Enhanced Shortest Path Routing (ESPR) d) Neighbour Exploring Routing (NER)

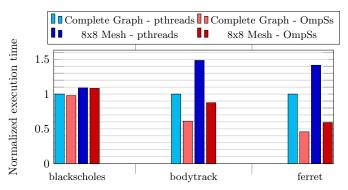

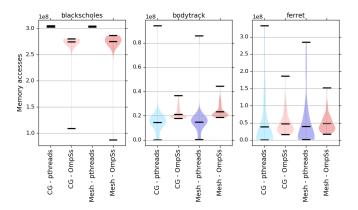

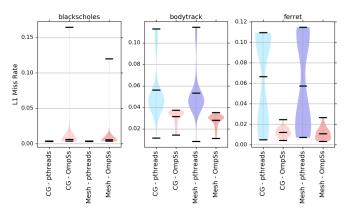

Fig. 6. Example of multicast trees for each algorithm. Legend: 'x' source, 'o' destinations, '\*' entry in routing table, '-' '|' '/' default route. From [5]